STM32英文参考手册_V15

Contents

Contents

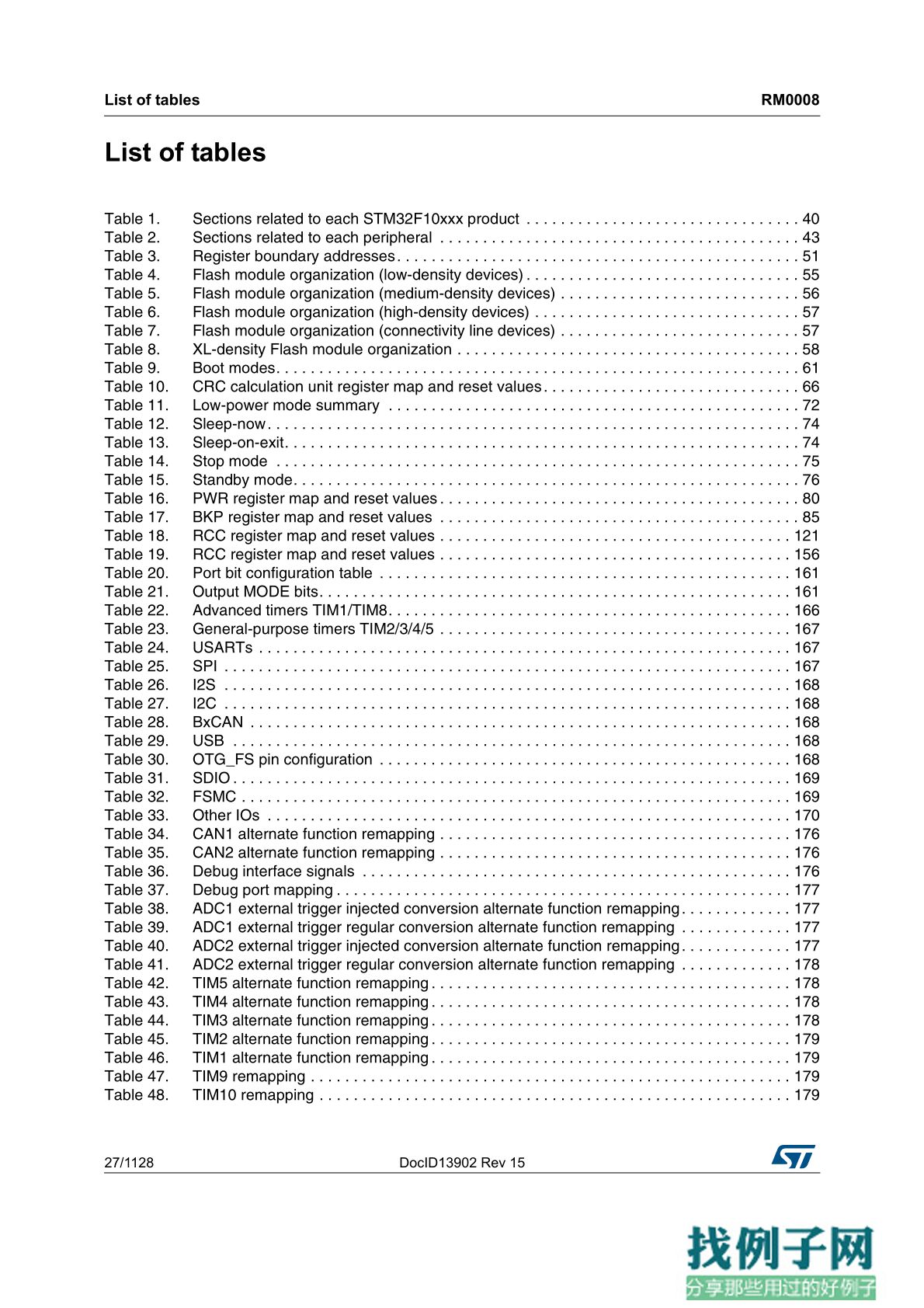

1 Overview of the manual . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

2 Documentation conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

2.1 List of abbreviations for registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

2.2 Glossary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

2.3 Peripheral availability . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

3 Memory and bus architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

3.1 System architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

3.2 Memory organization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

3.3 Memory map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

3.3.1 Embedded SRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

3.3.2 Bit banding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

3.3.3 Embedded Flash memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

3.4 Boot configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

4 CRC calculation unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

4.1 CRC introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

4.2 CRC main features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

4.3 CRC functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

4.4 CRC registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

4.4.1 Data register (CRC_DR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

4.4.2 Independent data register (CRC_IDR) . . . . . . . . . . . . . . . . . . . . . . . . . 65

4.4.3 Control register (CRC_CR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

4.4.4 CRC register map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

5 Power control (PWR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

5.1 Power supplies . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

5.1.1 Independent A/D and D/A converter supply and reference voltage . . . . 68

5.1.2 Battery backup domain . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

5.1.3 Voltage regulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

5.2 Power supply supervisor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

5.2.1 Power on reset (POR)/power down reset (PDR) . . . . . . . . . . . . . . . . . . 70

Contents RM0008

3/1128 DocID13902 Rev 15

5.2.2 Programmable voltage detector (PVD) . . . . . . . . . . . . . . . . . . . . . . . . . 70

5.3 Low-power modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

5.3.1 Slowing down system clocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

5.3.2 Peripheral clock gating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

5.3.3 Sleep mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

5.3.4 Stop mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

5.3.5 Standby mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

5.3.6 Auto-wakeup (AWU) from low-power mode . . . . . . . . . . . . . . . . . . . . . . 77

5.4 Power control registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

5.4.1 Power control register (PWR_CR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

5.4.2 Power control/status register (PWR_CSR) . . . . . . . . . . . . . . . . . . . . . . 79

5.4.3 PWR register map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

6 Backup registers (BKP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

6.1 BKP introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

6.2 BKP main features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

6.3 BKP functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

6.3.1 Tamper detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

6.3.2 RTC calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

6.4 BKP registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

6.4.1 Backup data register x (BKP_DRx) (x = 1 ..42) . . . . . . . . . . . . . . . . . . . 83

6.4.2 RTC clock calibration register (BKP_RTCCR) . . . . . . . . . . . . . . . . . . . . 83

6.4.3 Backup control register (BKP_CR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

6.4.4 Backup control/status register (BKP_CSR) . . . . . . . . . . . . . . . . . . . . . . 84

6.4.5 BKP register map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

7 Low-, medium-, high- and XL-density reset and clock

control (RCC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

7.1 Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

7.1.1 System reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

7.1.2 Power reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 91

7.1.3 Backup domain reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

7.2 Clocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

7.2.1 HSE clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

7.2.2 HSI clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

7.2.3 PLL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

DocID13902 Rev 15 4/1128

RM0008 Contents

26

7.2.4 LSE clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

7.2.5 LSI clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

7.2.6 System clock (SYSCLK) selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

7.2.7 Clock security system (CSS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

7.2.8 RTC clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

7.2.9 Watchdog clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

7.2.10 Clock-out capability . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

7.3 RCC registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

7.3.1 Clock control register (RCC_CR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

7.3.2 Clock configuration register (RCC_CFGR) . . . . . . . . . . . . . . . . . . . . . 101

7.3.3 Clock interrupt register (RCC_CIR) . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

7.3.4 APB2 peripheral reset register (RCC_APB2RSTR) . . . . . . . . . . . . . . 106

7.3.5 APB1 peripheral reset register (RCC_APB1RSTR) . . . . . . . . . . . . . . 109

7.3.6 AHB peripheral clock enable register (RCC_AHBENR) . . . . . . . . . . . 111

7.3.7 APB2 peripheral clock enable register (RCC_APB2ENR) . . . . . . . . . . 112

7.3.8 APB1 peripheral clock enable register (RCC_APB1ENR) . . . . . . . . . . 115

7.3.9 Backup domain control register (RCC_BDCR) . . . . . . . . . . . . . . . . . . 118

7.3.10 Control/status register (RCC_CSR) . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

7.3.11 RCC register map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

8 Connectivity line devices: reset and clock control (RCC) . . . . . . . . . 123

8.1 Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

8.1.1 System reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

8.1.2 Power reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

8.1.3 Backup domain reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

8.2 Clocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

8.2.1 HSE clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

8.2.2 HSI clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

8.2.3 PLLs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

8.2.4 LSE clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

8.2.5 LSI clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

8.2.6 System clock (SYSCLK) selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

8.2.7 Clock security system (CSS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

8.2.8 RTC clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

8.2.9 Watchdog clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

8.2.10 Clock-out capability . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 132

8.3 RCC registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 132

Contents RM0008

5/1128 DocID13902 Rev 15

8.3.1 Clock control register (RCC_CR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 132

8.3.2 Clock configuration register (RCC_CFGR) . . . . . . . . . . . . . . . . . . . . . 134

8.3.3 Clock interrupt register (RCC_CIR) . . . . . . . . . . . . . . . . . . . . . . . . . . . 137

8.3.4 APB2 peripheral reset register (RCC_APB2RSTR) . . . . . . . . . . . . . . 141

8.3.5 APB1 peripheral reset register (RCC_APB1RSTR) . . . . . . . . . . . . . . 142

8.3.6 AHB Peripheral Clock enable register (RCC_AHBENR) . . . . . . . . . . . 145

8.3.7 APB2 peripheral clock enable register (RCC_APB2ENR) . . . . . . . . . . 146

8.3.8 APB1 peripheral clock enable register (RCC_APB1ENR) . . . . . . . . . . 148

8.3.9 Backup domain control register (RCC_BDCR) . . . . . . . . . . . . . . . . . . 150

8.3.10 Control/status register (RCC_CSR) . . . . . . . . . . . . . . . . . . . . . . . . . . . 152

8.3.11 AHB peripheral clock reset register (RCC_AHBRSTR) . . . . . . . . . . . . 153

8.3.12 Clock configuration register2 (RCC_CFGR2) . . . . . . . . . . . . . . . . . . . 154

8.3.13 RCC register map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 156

9 General-purpose and alternate-function I/Os (GPIOs and AFIOs) . . 159

9.1 GPIO functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159

9.1.1 General-purpose I/O (GPIO) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

9.1.2 Atomic bit set or reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

9.1.3 External interrupt/wakeup lines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

9.1.4 Alternate functions (AF) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

9.1.5 Software remapping of I/O alternate functions . . . . . . . . . . . . . . . . . . 162

9.1.6 GPIO locking mechanism . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

9.1.7 Input configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163

9.1.8 Output configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164

9.1.9 Alternate function configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 165

9.1.10 Analog configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166

9.1.11 GPIO configurations for device peripherals . . . . . . . . . . . . . . . . . . . . . 166

9.2 GPIO registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171

9.2.1 Port configuration register low (GPIOx_CRL) (x=A..G) . . . . . . . . . . . . 171

9.2.2 Port configuration register high (GPIOx_CRH) (x=A..G) . . . . . . . . . . . 172

9.2.3 Port input data register (GPIOx_IDR) (x=A..G) . . . . . . . . . . . . . . . . . . 172

9.2.4 Port output data register (GPIOx_ODR) (x=A..G) . . . . . . . . . . . . . . . . 173

9.2.5 Port bit set/reset register (GPIOx_BSRR) (x=A..G) . . . . . . . . . . . . . . . 173

9.2.6 Port bit reset register (GPIOx_BRR) (x=A..G) . . . . . . . . . . . . . . . . . . . 174

9.2.7 Port configuration lock register (GPIOx_LCKR) (x=A..G) . . . . . . . . . . 174

9.3 Alternate function I/O and debug configuration (AFIO) . . . . . . . . . . . . . 175

9.3.1 Using OSC32_IN/OSC32_OUT pins as GPIO ports PC14/PC15 . . . . 175

DocID13902 Rev 15 6/1128

RM0008 Contents

26

9.3.2 Using OSC_IN/OSC_OUT pins as GPIO ports PD0/PD1 . . . . . . . . . . 175

9.3.3 CAN1 alternate function remapping . . . . . . . . . . . . . . . . . . . . . . . . . . . 176

9.3.4 CAN2 alternate function remapping . . . . . . . . . . . . . . . . . . . . . . . . . . . 176

9.3.5 JTAG/SWD alternate function remapping . . . . . . . . . . . . . . . . . . . . . . 176

9.3.6 ADC alternate function remapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . 177

9.3.7 Timer alternate function remapping . . . . . . . . . . . . . . . . . . . . . . . . . . . 178

9.3.8 USART alternate function remapping . . . . . . . . . . . . . . . . . . . . . . . . . 180

9.3.9 I2C1 alternate function remapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . 181

9.3.10 SPI1 alternate function remapping . . . . . . . . . . . . . . . . . . . . . . . . . . . 181

9.3.11 SPI3/I2S3 alternate function remapping . . . . . . . . . . . . . . . . . . . . . . . 181

9.3.12 Ethernet alternate function remapping . . . . . . . . . . . . . . . . . . . . . . . . 181

9.4 AFIO registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 183

9.4.1 Event control register (AFIO_EVCR) . . . . . . . . . . . . . . . . . . . . . . . . . . 183

9.4.2 AF remap and debug I/O configuration register (AFIO_MAPR) . . . . . . 184

9.4.3 External interrupt configuration register 1 (AFIO_EXTICR1) . . . . . . . . 191

9.4.4 External interrupt configuration register 2 (AFIO_EXTICR2) . . . . . . . . 191

9.4.5 External interrupt configuration register 3 (AFIO_EXTICR3) . . . . . . . . 192

9.4.6 External interrupt configuration register 4 (AFIO_EXTICR4) . . . . . . . . 192

9.4.7 AF remap and debug I/O configuration register2 (AFIO_MAPR2) . . . . 193

9.5 GPIO and AFIO register maps . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 194

10 Interrupts and events . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 196

10.1 Nested vectored interrupt controller (NVIC) . . . . . . . . . . . . . . . . . . . . . . 196

10.1.1 SysTick calibration value register . . . . . . . . . . . . . . . . . . . . . . . . . . . . 196

10.1.2 Interrupt and exception vectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 197

10.2 External interrupt/event controller (EXTI) . . . . . . . . . . . . . . . . . . . . . . . . 205

10.2.1 Main features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 206

10.2.2 Block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 206

10.2.3 Wakeup event management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 206

10.2.4 Functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 207

10.2.5 External interrupt/event line mapping . . . . . . . . . . . . . . . . . . . . . . . . . 208

10.3 EXTI registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 210

10.3.1 Interrupt mask register (EXTI_IMR) . . . . . . . . . . . . . . . . . . . . . . . . . . . 210

10.3.2 Event mask register (EXTI_EMR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 210

10.3.3 Rising trigger selection register (EXTI_RTSR) . . . . . . . . . . . . . . . . . . 211

10.3.4 Falling trigger selection register (EXTI_FTSR) . . . . . . . . . . . . . . . . . . 211

10.3.5 Software interrupt event register (EXTI_SWIER) . . . . . . . . . . . . . . . . . 212

Contents RM0008

7/1128 DocID13902 Rev 15

10.3.6 Pending register (EXTI_PR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 212

10.3.7 EXTI register map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 213

11 Analog-to-digital converter (ADC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 214

11.1 ADC introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 214

11.2 ADC main features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 215

11.3 ADC functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 215

11.3.1 ADC on-off control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 218

11.3.2 ADC clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 218

11.3.3 Channel selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 218

11.3.4 Single conversion mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 218

11.3.5 Continuous conversion mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 219

11.3.6 Timing diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 219

11.3.7 Analog watchdog . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 220

11.3.8 Scan mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 220

11.3.9 Injected channel management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 221

11.3.10 Discontinuous mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 222

11.4 Calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 222

11.5 Data alignment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 223

11.6 Channel-by-channel programmable sample time . . . . . . . . . . . . . . . . . . 224

11.7 Conversion on external trigger . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 224

11.8 DMA request . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 226

11.9 Dual ADC mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 227

11.9.1 Injected simultaneous mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 229

11.9.2 Regular simultaneous mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 229

11.9.3 Fast interleaved mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 230

11.9.4 Slow interleaved mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 230

11.9.5 Alternate trigger mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 231

11.9.6 Independent mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 232

11.9.7 Combined regular/injected simultaneous mode . . . . . . . . . . . . . . . . . . 232

11.9.8 Combined regular simultaneous alternate trigger mode . . . . . . . . . . 232

11.9.9 Combined injected simultaneous interleaved . . . . . . . . . . . . . . . . . . 233

11.10 Temperature sensor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 234

11.11 ADC interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 235

11.12 ADC registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 236

11.12.1 ADC status register (ADC_SR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 236

DocID13902 Rev 15 8/1128

RM0008 Contents

26

11.12.2 ADC control register 1 (ADC_CR1) . . . . . . . . . . . . . . . . . . . . . . . . . . . 237

11.12.3 ADC control register 2 (ADC_CR2) . . . . . . . . . . . . . . . . . . . . . . . . . . . 239

11.12.4 ADC sample time register 1 (ADC_SMPR1) . . . . . . . . . . . . . . . . . . . . 243

11.12.5 ADC sample time register 2 (ADC_SMPR2) . . . . . . . . . . . . . . . . . . . . 244

11.12.6 ADC injected channel data offset register x (ADC_JOFRx)(x=1..4) . . 244

11.12.7 ADC watchdog high threshold register (ADC_HTR) . . . . . . . . . . . . . . 245

11.12.8 ADC watchdog low threshold register (ADC_LTR) . . . . . . . . . . . . . . . 245

11.12.9 ADC regular sequence register 1 (ADC_SQR1) . . . . . . . . . . . . . . . . . 246

11.12.10 ADC regular sequence register 2 (ADC_SQR2) . . . . . . . . . . . . . . . . . 247

11.12.11 ADC regular sequence register 3 (ADC_SQR3) . . . . . . . . . . . . . . . . . 248

11.12.12 ADC injected sequence register (ADC_JSQR) . . . . . . . . . . . . . . . . . . 249

11.12.13 ADC injected data register x (ADC_JDRx) (x= 1..4) . . . . . . . . . . . . . . 250

11.12.14 ADC regular data register (ADC_DR) . . . . . . . . . . . . . . . . . . . . . . . . . 250

11.12.15 ADC register map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 251

12 Digital-to-analog converter (DAC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 253

12.1 DAC introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 253

12.2 DAC main features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 253

12.3 DAC functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 255

12.3.1 DAC channel enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 255

12.3.2 DAC output buffer enable . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 255

12.3.3 DAC data format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 255

12.3.4 DAC conversion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 256

12.3.5 DAC output voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 257

12.3.6 DAC trigger selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 257

12.3.7 DMA request . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 258

12.3.8 Noise generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 258

12.3.9 Triangle-wave generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 259

12.4 Dual DAC channel conversion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 260

12.4.1 Independent trigger without wave generation . . . . . . . . . . . . . . . . . . . 260

12.4.2 Independent trigger with same LFSR generation . . . . . . . . . . . . . . . . 261

12.4.3 Independent trigger with different LFSR generation . . . . . . . . . . . . . . 261

12.4.4 Independent trigger with same triangle generation . . . . . . . . . . . . . . . 261

12.4.5 Independent trigger with different triangle generation . . . . . . . . . . . . . 262

12.4.6 Simultaneous software start . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 262

12.4.7 Simultaneous trigger without wave generation . . . . . . . . . . . . . . . . . . 262

12.4.8 Simultaneous trigger with same LFSR generation . . . . . . . . . . . . . . . 263

Contents RM0008

9/1128 DocID13902 Rev 15

12.4.9 Simultaneous trigger with different LFSR generation . . . . . . . . . . . . . 263

12.4.10 Simultaneous trigger with same triangle generation . . . . . . . . . . . . . . 263

12.4.11 Simultaneous trigger with different triangle generation . . . . . . . . . . . . 264

12.5 DAC registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 264

12.5.1 DAC control register (DAC_CR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 264

12.5.2 DAC software trigger register (DAC_SWTRIGR) . . . . . . . . . . . . . . . . . 267

12.5.3 DAC channel1 12-bit right-aligned data holding register

(DAC_DHR12R1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 268

12.5.4 DAC channel1 12-bit left aligned data holding register

(DAC_DHR12L1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 268

12.5.5 DAC channel1 8-bit right aligned data holding register

(DAC_DHR8R1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 268

12.5.6 DAC channel2 12-bit right aligned data holding register

(DAC_DHR12R2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 269

12.5.7 DAC channel2 12-bit left aligned data holding register

(DAC_DHR12L2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 269

12.5.8 DAC channel2 8-bit right-aligned data holding register

(DAC_DHR8R2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 269

12.5.9 Dual DAC 12-bit right-aligned data holding register

(DAC_DHR12RD) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 270

12.5.10 DUAL DAC 12-bit left aligned data holding register

(DAC_DHR12LD) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 270

12.5.11 DUAL DAC 8-bit right aligned data holding register

(DAC_DHR8RD) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 271

12.5.12 DAC channel1 data output register (DAC_DOR1) . . . . . . . . . . . . . . . . 271

12.5.13 DAC channel2 data output register (DAC_DOR2) . . . . . . . . . . . . . . . . 271

12.5.14 DAC register map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 272

13 Direct memory access controller (DMA) . . . . . . . . . . . . . . . . . . . . . . . 273

13.1 DMA introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 273

13.2 DMA main features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 273

13.3 DMA functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 275

13.3.1 DMA transactions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 275

13.3.2 Arbiter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 276

13.3.3 DMA channels . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 276

13.3.4 Programmable data width, data alignment and endians . . . . . . . . . . . 278

13.3.5 Error management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 279

13.3.6 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 280

13.3.7 DMA request mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 280

DocID13902 Rev 15 10/1128

RM0008 Contents

26

13.4 DMA registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 284

13.4.1 DMA interrupt status register (DMA_ISR) . . . . . . . . . . . . . . . . . . . . . . 284

13.4.2 DMA interrupt flag clear register (DMA_IFCR) . . . . . . . . . . . . . . . . . . 285

13.4.3 DMA channel x configuration register (DMA_CCRx) (x = 1..7,

where x = channel number) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 286

13.4.4 DMA channel x number of data register (DMA_CNDTRx) (x = 1..7),

where x = channel number) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 287

13.4.5 DMA channel x peripheral address register (DMA_CPARx) (x = 1..7),

where x = channel number) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 288

13.4.6 DMA channel x memory address register (DMA_CMARx) (x = 1..7),

where x = channel number) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 288

13.4.7 DMA register map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 289

14 Advanced-control timers (TIM1&TIM8) . . . . . . . . . . . . . . . . . . . . . . . . 292

14.1 TIM1&TIM8 introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 292

14.2 TIM1&TIM8 main features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 293

14.3 TIM1&TIM8 functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 295

14.3.1 Time-base unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 295

14.3.2 Counter modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 296

14.3.3 Repetition counter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 304

14.3.4 Clock selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 306

14.3.5 Capture/compare channels . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 308

14.3.6 Input capture mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 310

14.3.7 PWM input mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 311

14.3.8 Forced output mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 312

14.3.9 Output compare mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 313

14.3.10 PWM mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 314

14.3.11 Complementary outputs and dead-time insertion . . . . . . . . . . . . . . . . 317

14.3.12 Using the break function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 318

14.3.13 Clearing the OCxREF signal on an external event . . . . . . . . . . . . . . . 321

14.3.14 6-step PWM generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 322

14.3.15 One-pulse mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 323

14.3.16 Encoder interface mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 324

14.3.17 Timer input XOR function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 326

14.3.18 Interfacing with Hall sensors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 327

14.3.19 TIMx and external trigger synchronization . . . . . . . . . . . . . . . . . . . . . . 329

14.3.20 Timer synchronization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 332

14.3.21 Debug mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 332

Contents RM0008

11/1128 DocID13902 Rev 15

14.4 TIM1&TIM8 registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 333

14.4.1 TIM1&TIM8 control register 1 (TIMx_CR1) . . . . . . . . . . . . . . . . . . . . . 333

14.4.2 TIM1&TIM8 control register 2 (TIMx_CR2) . . . . . . . . . . . . . . . . . . . . . 334

14.4.3 TIM1&TIM8 slave mode control register (TIMx_SMCR) . . . . . . . . . . . 337

14.4.4 TIM1&TIM8 DMA/interrupt enable register (TIMx_DIER) . . . . . . . . . . 339

14.4.5 TIM1&TIM8 status register (TIMx_SR) . . . . . . . . . . . . . . . . . . . . . . . . 341

14.4.6 TIM1&TIM8 event generation register (TIMx_EGR) . . . . . . . . . . . . . . 342

14.4.7 TIM1&TIM8 capture/compare mode register 1 (TIMx_CCMR1) . . . . . 344

14.4.8 TIM1&TIM8 capture/compare mode register 2 (TIMx_CCMR2) . . . . . 347

14.4.9 TIM1&TIM8 capture/compare enable register (TIMx_CCER) . . . . . . . 348

14.4.10 TIM1&TIM8 counter (TIMx_CNT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 351

14.4.11 TIM1&TIM8 prescaler (TIMx_PSC) . . . . . . . . . . . . . . . . . . . . . . . . . . . 351

14.4.12 TIM1&TIM8 auto-reload register (TIMx_ARR) . . . . . . . . . . . . . . . . . . . 351

14.4.13 TIM1&TIM8 repetition counter register (TIMx_RCR) . . . . . . . . . . . . . . 352

14.4.14 TIM1&TIM8 capture/compare register 1 (TIMx_CCR1) . . . . . . . . . . . . 352

14.4.15 TIM1&TIM8 capture/compare register 2 (TIMx_CCR2) . . . . . . . . . . . . 353

14.4.16 TIM1&TIM8 capture/compare register 3 (TIMx_CCR3) . . . . . . . . . . . . 353

14.4.17 TIM1&TIM8 capture/compare register 4 (TIMx_CCR4) . . . . . . . . . . . . 354

14.4.18 TIM1&TIM8 break and dead-time register (TIMx_BDTR) . . . . . . . . . . 354

14.4.19 TIM1&TIM8 DMA control register (TIMx_DCR) . . . . . . . . . . . . . . . . . . 356

14.4.20 TIM1&TIM8 DMA address for full transfer (TIMx_DMAR) . . . . . . . . . . 357

14.4.21 TIM1&TIM8 register map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 358

15 General-purpose timers (TIM2 to TIM5) . . . . . . . . . . . . . . . . . . . . . . . . 360

15.1 TIM2 to TIM5 introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 360

15.2 TIMx main features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 361

15.3 TIMx functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 362

15.3.1 Time-base unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 362

15.3.2 Counter modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 364

15.3.3 Clock selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 372

15.3.4 Capture/compare channels . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 375

15.3.5 Input capture mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 377

15.3.6 PWM input mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 378

15.3.7 Forced output mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 379

15.3.8 Output compare mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 379

15.3.9 PWM mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 380

15.3.10 One-pulse mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 383

DocID13902 Rev 15 12/1128

RM0008 Contents

26

15.3.11 Clearing the OCxREF signal on an external event . . . . . . . . . . . . . . . 384

15.3.12 Encoder interface mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 385

15.3.13 Timer input XOR function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 388

15.3.14 Timers and external trigger synchronization . . . . . . . . . . . . . . . . . . . . 388

15.3.15 Timer synchronization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 391

15.3.16 Debug mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 396

15.4 TIMx2 to TIM5 registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 397

15.4.1 TIMx control register 1 (TIMx_CR1) . . . . . . . . . . . . . . . . . . . . . . . . . . 397

15.4.2 TIMx control register 2 (TIMx_CR2) . . . . . . . . . . . . . . . . . . . . . . . . . . 399

15.4.3 TIMx slave mode control register (TIMx_SMCR) . . . . . . . . . . . . . . . . . 400

15.4.4 TIMx DMA/Interrupt enable register (TIMx_DIER) . . . . . . . . . . . . . . . . 402

15.4.5 TIMx status register (TIMx_SR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 403

15.4.6 TIMx event generation register (TIMx_EGR) . . . . . . . . . . . . . . . . . . . . 405

15.4.7 TIMx capture/compare mode register 1 (TIMx_CCMR1) . . . . . . . . . . . 406

15.4.8 TIMx capture/compare mode register 2 (TIMx_CCMR2) . . . . . . . . . . . 409

15.4.9 TIMx capture/compare enable register (TIMx_CCER) . . . . . . . . . . . . . 410

15.4.10 TIMx counter (TIMx_CNT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 411

15.4.11 TIMx prescaler (TIMx_PSC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 412

15.4.12 TIMx auto-reload register (TIMx_ARR) . . . . . . . . . . . . . . . . . . . . . . . . 412

15.4.13 TIMx capture/compare register 1 (TIMx_CCR1) . . . . . . . . . . . . . . . . . 412

15.4.14 TIMx capture/compare register 2 (TIMx_CCR2) . . . . . . . . . . . . . . . . . 413

15.4.15 TIMx capture/compare register 3 (TIMx_CCR3) . . . . . . . . . . . . . . . . . 413

15.4.16 TIMx capture/compare register 4 (TIMx_CCR4) . . . . . . . . . . . . . . . . . 413

15.4.17 TIMx DMA control register (TIMx_DCR) . . . . . . . . . . . . . . . . . . . . . . . 414

15.4.18 TIMx DMA address for full transfer (TIMx_DMAR) . . . . . . . . . . . . . . . 414

15.4.19 TIMx register map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 416

16 General-purpose timers (TIM9 to TIM14) . . . . . . . . . . . . . . . . . . . . . . . 418

16.1 TIM9 to TIM14 introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 418

16.2 TIM9 to TIM14 main features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 419

16.2.1 TIM9/TIM12 main features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 419

16.2.2 TIM10/TIM11 and TIM13/TIM14 main features . . . . . . . . . . . . . . . . . . 420

16.3 TIM9 to TIM14 functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . 421

16.3.1 Time-base unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 421

16.3.2 Counter modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 422

16.3.3 Clock selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 425

16.3.4 Capture/compare channels . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 427

Contents RM0008

13/1128 DocID13902 Rev 15

16.3.5 Input capture mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 428

16.3.6 PWM input mode (only for TIM9/12) . . . . . . . . . . . . . . . . . . . . . . . . . . 429

16.3.7 Forced output mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 430

16.3.8 Output compare mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 431

16.3.9 PWM mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 432

16.3.10 One-pulse mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 433

16.3.11 TIM9/12 external trigger synchronization . . . . . . . . . . . . . . . . . . . . . . . 434

16.3.12 Timer synchronization (TIM9/12) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 437

16.3.13 Debug mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 437

16.4 TIM9 and TIM12 registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 437

16.4.1 TIM9/12 control register 1 (TIMx_CR1) . . . . . . . . . . . . . . . . . . . . . . . . 437

16.4.2 9/12TIM9/12 slave mode control register (TIMx_SMCR) . . . . . . . . . . . 439

16.4.3 TIM9/12 Interrupt enable register (TIMx_DIER) . . . . . . . . . . . . . . . . . 440

16.4.4 TIM9/12 status register (TIMx_SR) . . . . . . . . . . . . . . . . . . . . . . . . . . . 441

16.4.5 TIM9/12 event generation register (TIMx_EGR) . . . . . . . . . . . . . . . . . 442

16.4.6 TIM9/12 capture/compare mode register 1 (TIMx_CCMR1) . . . . . . . . 444

16.4.7 TIM9/12 capture/compare enable register (TIMx_CCER) . . . . . . . . . . 447

16.4.8 TIM9/12 counter (TIMx_CNT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 448

16.4.9 TIM9/12 prescaler (TIMx_PSC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 448

16.4.10 TIM9/12 auto-reload register (TIMx_ARR) . . . . . . . . . . . . . . . . . . . . . 448

16.4.11 TIM9/12 capture/compare register 1 (TIMx_CCR1) . . . . . . . . . . . . . . 449

16.4.12 TIM9/12 capture/compare register 2 (TIMx_CCR2) . . . . . . . . . . . . . . 449

16.4.13 TIM9/12 register map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 449

16.5 TIM10/11/13/14 registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 452

16.5.1 TIM10/11/13/14 control register 1 (TIMx_CR1) . . . . . . . . . . . . . . . . . . 452

16.5.2 TIM10/11/13/14 status register (TIMx_SR) . . . . . . . . . . . . . . . . . . . . . 453

16.5.3 TIM10/11/13/14 event generation register (TIMx_EGR) . . . . . . . . . . . 453

16.5.4 TIM10/11/13/14 capture/compare mode register 1

(TIMx_CCMR1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 454

16.5.5 TIM10/11/13/14 capture/compare enable register

(TIMx_CCER) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 457

16.5.6 TIM10/11/13/14 counter (TIMx_CNT) . . . . . . . . . . . . . . . . . . . . . . . . . 458

16.5.7 TIM10/11/13/14 prescaler (TIMx_PSC) . . . . . . . . . . . . . . . . . . . . . . . . 458

16.5.8 TIM10/11/13/14 auto-reload register (TIMx_ARR) . . . . . . . . . . . . . . . 458

16.5.9 TIM10/11/13/14 capture/compare register 1 (TIMx_CCR1) . . . . . . . . 459

16.5.10 TIM10/11/13/14 register map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 459

DocID13902 Rev 15 14/1128

RM0008 Contents

26

17 Basic timers (TIM6&TIM7) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 461

17.1 TIM6&TIM7 introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 461

17.2 TIM6&TIM7 main features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 461

17.3 TIM6&TIM7 functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 462

17.3.1 Time-base unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 462

17.3.2 Counting mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 464

17.3.3 Clock source . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 466

17.3.4 Debug mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 467

17.4 TIM6&TIM7 registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 467

17.4.1 TIM6&TIM7 control register 1 (TIMx_CR1) . . . . . . . . . . . . . . . . . . . . . 467

17.4.2 TIM6&TIM7 control register 2 (TIMx_CR2) . . . . . . . . . . . . . . . . . . . . . 469

17.4.3 TIM6&TIM7 DMA/Interrupt enable register (TIMx_DIER) . . . . . . . . . . 469

17.4.4 TIM6&TIM7 status register (TIMx_SR) . . . . . . . . . . . . . . . . . . . . . . . . 470

17.4.5 TIM6&TIM7 event generation register (TIMx_EGR) . . . . . . . . . . . . . . 470

17.4.6 TIM6&TIM7 counter (TIMx_CNT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 470

17.4.7 TIM6&TIM7 prescaler (TIMx_PSC) . . . . . . . . . . . . . . . . . . . . . . . . . . . 471

17.4.8 TIM6&TIM7 auto-reload register (TIMx_ARR) . . . . . . . . . . . . . . . . . . . 471

17.4.9 TIM6&TIM7 register map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 472

18 Real-time clock (RTC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 473

18.1 RTC introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 473

18.2 RTC main features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 474

18.3 RTC functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 475

18.3.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 475

18.3.2 Resetting RTC registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 476

18.3.3 Reading RTC registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 476

18.3.4 Configuring RTC registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 476

18.3.5 RTC flag assertion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 477

18.4 RTC registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 478

18.4.1 RTC control register high (RTC_CRH) . . . . . . . . . . . . . . . . . . . . . . . . 478

18.4.2 RTC control register low (RTC_CRL) . . . . . . . . . . . . . . . . . . . . . . . . . . 479

18.4.3 RTC prescaler load register (RTC_PRLH / RTC_PRLL) . . . . . . . . . . . 480

18.4.4 RTC prescaler divider register (RTC_DIVH / RTC_DIVL) . . . . . . . . . . 481

18.4.5 RTC counter register (RTC_CNTH / RTC_CNTL) . . . . . . . . . . . . . . . . 482

18.4.6 RTC alarm register high (RTC_ALRH / RTC_ALRL) . . . . . . . . . . . . . . 483

18.4.7 RTC register map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 484

Contents RM0008

15/1128 DocID13902 Rev 15

19 Independent watchdog (IWDG) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 485

19.1 IWDG introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 485

19.2 IWDG main features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 485

19.3 IWDG functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 485

19.3.1 Hardware watchdog . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 486

19.3.2 Register access protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 486

19.3.3 Debug mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 486

19.4 IWDG registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 487

19.4.1 Key register (IWDG_KR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 487

19.4.2 Prescaler register (IWDG_PR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 488

19.4.3 Reload register (IWDG_RLR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 488

19.4.4 Status register (IWDG_SR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 488

19.4.5 IWDG register map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 490

20 Window watchdog (WWDG) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 491

20.1 WWDG introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 491

20.2 WWDG main features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 491

20.3 WWDG functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 491

20.4 How to program the watchdog timeout . . . . . . . . . . . . . . . . . . . . . . . . . . 493

20.5 Debug mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 494

20.6 WWDG registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 495

20.6.1 Control register (WWDG_CR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 495

20.6.2 Configuration register (WWDG_CFR) . . . . . . . . . . . . . . . . . . . . . . . . . 496

20.6.3 Status register (WWDG_SR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 496

20.6.4 WWDG register map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 497

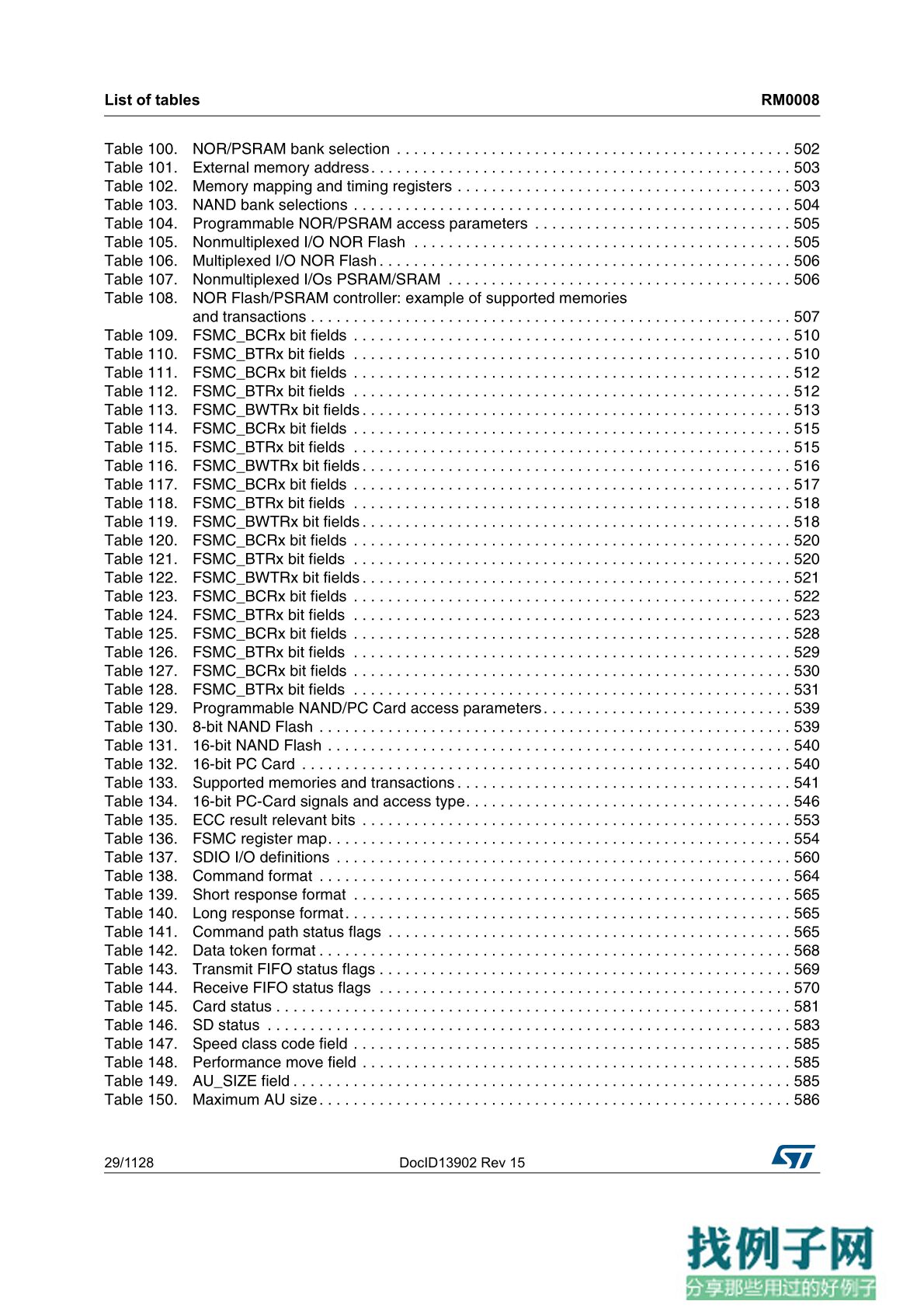

21 Flexible static memory controller (FSMC) . . . . . . . . . . . . . . . . . . . . . 498

21.1 FSMC main features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 498

21.2 Block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 499

21.3 AHB interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 500

21.3.1 Supported memories and transactions . . . . . . . . . . . . . . . . . . . . . . . . 501

21.4 External device address mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 502

21.4.1 NOR/PSRAM address mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 502

21.4.2 NAND/PC Card address mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . 503

21.5 NOR Flash/PSRAM controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 504

DocID13902 Rev 15 16/1128

RM0008 Contents

26

21.5.1 External memory interface signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . 505

21.5.2 Supported memories and transactions . . . . . . . . . . . . . . . . . . . . . . . . 506

21.5.3 General timing rules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 508

21.5.4 NOR Flash/PSRAM controller asynchronous transactions . . . . . . . . . 508

21.5.5 Synchronous transactions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 526

21.5.6 NOR/PSRAM control registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 532

21.6 NAND Flash/PC Card controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 538

21.6.1 External memory interface signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . 539

21.6.2 NAND Flash / PC Card supported memories and transactions . . . . . . 541

21.6.3 Timing diagrams for NAND and PC Card . . . . . . . . . . . . . . . . . . . . . . 541

21.6.4 NAND Flash operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 542

21.6.5 NAND Flash pre-wait functionality . . . . . . . . . . . . . . . . . . . . . . . . . . . . 543

21.6.6 Computation of the error correction code (ECC)

in NAND Flash memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 544

21.6.7 PC Card/CompactFlash operations . . . . . . . . . . . . . . . . . . . . . . . . . . . 545

21.6.8 NAND Flash/PC Card control registers . . . . . . . . . . . . . . . . . . . . . . . . 547

21.6.9 FSMC register map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 554

22 Secure digital input/output interface (SDIO) . . . . . . . . . . . . . . . . . . . . 556

22.1 SDIO main features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 556

22.2 SDIO bus topology . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 557

22.3 SDIO functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 559

22.3.1 SDIO adapter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 560

22.3.2 SDIO AHB interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 570

22.4 Card functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 571

22.4.1 Card identification mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 571

22.4.2 Card reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 571

22.4.3 Operating voltage range validation . . . . . . . . . . . . . . . . . . . . . . . . . . . 572

22.4.4 Card identification process . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 572

22.4.5 Block write . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 573

22.4.6 Block read . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 574

22.4.7 Stream access, stream write and stream read (MultiMediaCard only) 574

22.4.8 Erase: group erase and sector erase . . . . . . . . . . . . . . . . . . . . . . . . . . 576

22.4.9 Wide bus selection or deselection . . . . . . . . . . . . . . . . . . . . . . . . . . . . 577

22.4.10 Protection management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 577

22.4.11 Card status register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 580

22.4.12 SD status register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 583

Contents RM0008

17/1128 DocID13902 Rev 15

22.4.13 SD I/O mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 587

22.4.14 Commands and responses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 588

22.5 Response formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 591

22.5.1 R1 (normal response command) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 592

22.5.2 R1b . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 592

22.5.3 R2 (CID, CSD register) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 592

22.5.4 R3 (OCR register) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 592

22.5.5 R4 (Fast I/O) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 593

22.5.6 R4b . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 593

22.5.7 R5 (interrupt request) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 594

22.5.8 R6 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 594

22.6 SDIO I/O card-specific operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 595

22.6.1 SDIO I/O read wait operation by SDIO_D2 signalling . . . . . . . . . . . . . 595

22.6.2 SDIO read wait operation by stopping SDIO_CK . . . . . . . . . . . . . . . . 595

22.6.3 SDIO suspend/resume operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . 596

22.6.4 SDIO interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 596

22.7 CE-ATA specific operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 596

22.7.1 Command completion signal disable . . . . . . . . . . . . . . . . . . . . . . . . . . 596

22.7.2 Command completion signal enable . . . . . . . . . . . . . . . . . . . . . . . . . . 596

22.7.3 CE-ATA interrupt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 597

22.7.4 Aborting CMD61 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 597

22.8 HW flow control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 597

22.9 SDIO registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 597

22.9.1 SDIO power control register (SDIO_POWER) . . . . . . . . . . . . . . . . . . . 598

22.9.2 SDI clock control register (SDIO_CLKCR) . . . . . . . . . . . . . . . . . . . . . . 598

22.9.3 SDIO argument register (SDIO_ARG) . . . . . . . . . . . . . . . . . . . . . . . . . 599

22.9.4 SDIO command register (SDIO_CMD) . . . . . . . . . . . . . . . . . . . . . . . . 600

22.9.5 SDIO command response register (SDIO_RESPCMD) . . . . . . . . . . . 601

22.9.6 SDIO response 1..4 register (SDIO_RESPx) . . . . . . . . . . . . . . . . . . . 601

22.9.7 SDIO data timer register (SDIO_DTIMER) . . . . . . . . . . . . . . . . . . . . . 602

22.9.8 SDIO data length register (SDIO_DLEN) . . . . . . . . . . . . . . . . . . . . . . 602

22.9.9 SDIO data control register (SDIO_DCTRL) . . . . . . . . . . . . . . . . . . . . . 603

22.9.10 SDIO data counter register (SDIO_DCOUNT) . . . . . . . . . . . . . . . . . . 604

22.9.11 SDIO status register (SDIO_STA) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 605

22.9.12 SDIO interrupt clear register (SDIO_ICR) . . . . . . . . . . . . . . . . . . . . . . 606

22.9.13 SDIO mask register (SDIO_MASK) . . . . . . . . . . . . . . . . . . . . . . . . . . . 608

DocID13902 Rev 15 18/1128

RM0008 Contents

26

22.9.14 SDIO FIFO counter register (SDIO_FIFOCNT) . . . . . . . . . . . . . . . . . . 610

22.9.15 SDIO data FIFO register (SDIO_FIFO) . . . . . . . . . . . . . . . . . . . . . . . . 611

22.9.16 SDIO register map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 611

23 Universal serial bus full-speed device interface (USB) . . . . . . . . . . . 613

23.1 USB introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 613

23.2 USB main features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 613

23.3 USB functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 613

23.3.1 Description of USB blocks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 615

23.4 Programming considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 616

23.4.1 Generic USB device programming . . . . . . . . . . . . . . . . . . . . . . . . . . . 616

23.4.2 System and power-on reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 617

23.4.3 Double-buffered endpoints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 621

23.4.4 Isochronous transfers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 625

23.4.5 Suspend/Resume events . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 626

23.5 USB registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 628

23.5.1 Common registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 628

23.5.2 Endpoint-specific registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 635

23.5.3 Buffer descriptor table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 640

23.5.4 USB register map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 643

24 Controller area network (bxCAN) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 645

24.1 bxCAN introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 645

24.2 bxCAN main features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 645

24.3 bxCAN general description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 646

24.3.1 CAN 2.0B active core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 647

24.3.2 Control, status and configuration registers . . . . . . . . . . . . . . . . . . . . . 647

24.3.3 Tx mailboxes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 647

24.3.4 Acceptance filters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 647

24.4 bxCAN operating modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 648

24.4.1 Initialization mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 649

24.4.2 Normal mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 649

24.4.3 Sleep mode (low power) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 649

24.5 Test mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 650

24.5.1 Silent mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 650

24.5.2 Loop back mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 651

Contents RM0008

19/1128 DocID13902 Rev 15

24.5.3 Loop back combined with silent mode . . . . . . . . . . . . . . . . . . . . . . . . . 651

24.6 Debug mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 652

24.7 bxCAN functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 652

24.7.1 Transmission handling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 652

24.7.2 Time triggered communication mode . . . . . . . . . . . . . . . . . . . . . . . . . 654

24.7.3 Reception handling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 654

24.7.4 Identifier filtering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 655

24.7.5 Message storage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 659

24.7.6 Error management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 661

24.7.7 Bit timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 661

24.8 bxCAN interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 663

24.9 CAN registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 665

24.9.1 Register access protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 665

24.9.2 CAN control and status registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 665

24.9.3 CAN mailbox registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 675

24.9.4 CAN filter registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 682

24.9.5 bxCAN register map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 686

25 Serial peripheral interface (SPI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 690

25.1 SPI introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 690

25.2 SPI and I 2 S main features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 691

25.2.1 SPI features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 691

25.2.2 I 2 S features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 692

25.3 SPI functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 693

25.3.1 General description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 693

25.3.2 Configuring the SPI in slave mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . 696

25.3.3 Configuring the SPI in master mode . . . . . . . . . . . . . . . . . . . . . . . . . . 698

25.3.4 Configuring the SPI for half-duplex communication . . . . . . . . . . . . . . . 699

25.3.5 Data transmission and reception procedures . . . . . . . . . . . . . . . . . . . 699

25.3.6 CRC calculation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 706

25.3.7 Status flags . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 708

25.3.8 Disabling the SPI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 709

25.3.9 SPI communication using DMA (direct memory addressing) . . . . . . . 710

25.3.10 Error flags . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 712

25.3.11 SPI interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 713

25.4 I 2 S functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 714

DocID13902 Rev 15 20/1128

RM0008 Contents

26

25.4.1 I 2 S general description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 714

25.4.2 Supported audio protocols . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 715

25.4.3 Clock generator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 722

25.4.4 I 2 S master mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 727

25.4.5 I 2 S slave mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 728

25.4.6 Status flags . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 730

25.4.7 Error flags . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 731

25.4.8 I 2 S interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 732

25.4.9 DMA features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 732

25.5 SPI and I 2 S registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 733

25.5.1 SPI control register 1 (SPI_CR1) (not used in I 2 S mode) . . . . . . . . . . 733

25.5.2 SPI control register 2 (SPI_CR2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 735

25.5.3 SPI status register (SPI_SR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 736

25.5.4 SPI data register (SPI_DR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 737

25.5.5 SPI CRC polynomial register (SPI_CRCPR) (not used in I 2 S

mode) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 738

25.5.6 SPI RX CRC register (SPI_RXCRCR) (not used in I 2 S mode) . . . . . . 738

25.5.7 SPI TX CRC register (SPI_TXCRCR) (not used in I 2 S mode) . . . . . . 738

25.5.8 SPI_I 2 S configuration register (SPI_I2SCFGR) . . . . . . . . . . . . . . . . . . 739

25.5.9 SPI_I 2 S prescaler register (SPI_I2SPR) . . . . . . . . . . . . . . . . . . . . . . . 740

25.5.10 SPI register map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 742

26 Inter-integrated circuit (I 2 C) interface . . . . . . . . . . . . . . . . . . . . . . . . . 743

26.1 I 2 C introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 743

26.2 I 2 C main features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 744

26.3 I 2 C functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 745

26.3.1 Mode selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 745

26.3.2 I2C slave mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 746

26.3.3 I2C master mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 749

26.3.4 Error conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 757

26.3.5 SDA/SCL line control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 758

26.3.6 SMBus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 759

26.3.7 DMA requests . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 761

26.3.8 Packet error checking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 763

26.4 I 2 C interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 763

26.5 I 2 C debug mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 765

26.6 I 2 C registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 765

Contents RM0008

21/1128 DocID13902 Rev 15

26.6.1 I 2 C Control register 1 (I2C_CR1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 765

26.6.2 I 2 C Control register 2 (I2C_CR2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 767

26.6.3 I 2 C Own address register 1 (I2C_OAR1) . . . . . . . . . . . . . . . . . . . . . . . 769

26.6.4 I 2 C Own address register 2 (I2C_OAR2) . . . . . . . . . . . . . . . . . . . . . . . 769

26.6.5 I 2 C Data register (I2C_DR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 770

26.6.6 I 2 C Status register 1 (I2C_SR1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 770

26.6.7 I 2 C Status register 2 (I2C_SR2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 774

26.6.8 I 2 C Clock control register (I2C_CCR) . . . . . . . . . . . . . . . . . . . . . . . . . 775

26.6.9 I 2 C TRISE register (I2C_TRISE) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 776

26.6.10 I2C register map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 777

27 Universal synchronous asynchronous receiver

transmitter (USART) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 778

27.1 USART introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 778

27.2 USART main features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 779

27.3 USART functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 780

27.3.1 USART character description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 783

27.3.2 Transmitter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 784

27.3.3 Receiver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 787

27.3.4 Fractional baud rate generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 791

27.3.5 USART receiver’s tolerance to clock deviation . . . . . . . . . . . . . . . . . . 793

27.3.6 Multiprocessor communication . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 793

27.3.7 Parity control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 795

27.3.8 LIN (local interconnection network) mode . . . . . . . . . . . . . . . . . . . . . . 796

27.3.9 USART synchronous mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 798

27.3.10 Single-wire half-duplex communication . . . . . . . . . . . . . . . . . . . . . . . . 800

27.3.11 Smartcard . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 801

27.3.12 IrDA SIR ENDEC block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 803

27.3.13 Continuous communication using DMA . . . . . . . . . . . . . . . . . . . . . . . . 805

27.3.14 Hardware flow control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 808

27.4 USART interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 809

27.5 USART mode configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 810

27.6 USART registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 810

27.6.1 Status register (USART_SR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 811

27.6.2 Data register (USART_DR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 813

27.6.3 Baud rate register (USART_BRR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 813

27.6.4 Control register 1 (USART_CR1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 814

DocID13902 Rev 15 22/1128

RM0008 Contents

26

27.6.5 Control register 2 (USART_CR2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 816

27.6.6 Control register 3 (USART_CR3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 817

27.6.7 Guard time and prescaler register (USART_GTPR) . . . . . . . . . . . . . . 819

27.6.8 USART register map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 820

28 USB on-the-go full-speed (OTG_FS) . . . . . . . . . . . . . . . . . . . . . . . . . . 821

28.1 OTG_FS introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 821

28.2 OTG_FS main features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 822

28.2.1 General features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 822

28.2.2 Host-mode features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 823

28.2.3 Peripheral-mode features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 823

28.3 OTG_FS functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 824

28.3.1 OTG full-speed core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 824

28.3.2 Full-speed OTG PHY . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 824

28.4 OTG dual role device (DRD) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 825

28.4.1 ID line detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 826

28.4.2 HNP dual role device . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 826

28.4.3 SRP dual role device . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 826

28.5 USB peripheral . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 827

28.5.1 SRP-capable peripheral . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 827

28.5.2 Peripheral states . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 828

28.5.3 Peripheral endpoints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 829

28.6 USB host . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 831

28.6.1 SRP-capable host . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 832

28.6.2 USB host states . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 832

28.6.3 Host channels . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 834

28.6.4 Host scheduler . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 835

28.7 SOF trigger . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 836

28.7.1 Host SOFs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 836

28.7.2 Peripheral SOFs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 836

28.8 Power options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 837

28.9 Dynamic update of the OTG_FS_HFIR register . . . . . . . . . . . . . . . . . . . 838

28.10 USB data FIFOs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 838